あなたはをフォローしました

ユーザーのフォローエラー。

このユーザーはフォローを許可していません。

このユーザーをすでにフォローしています。

あなたのメンバーシッププランは、0 個のフォローのみ許可します。アップグレードは、 こちら。

のフォローを解除しました

ユーザーのフォロー解除エラー。

あなたはを推薦しました

ユーザーの推薦エラー。

何か問題が発生しました。ページを更新してもう一度お試しください。

仕事についてLoi L.に連絡する

ログインしてチャットで詳細を相談しましょう、

ポートフォリオ

ポートフォリオ

Quadcopter Controller Board

Quadcopter Controller Board

Magnet Controller using Android Apps - Shipped to US

Universal Remote + Camera + Wifi Module

Universal Remote + Camera + Wifi Module

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

4-Layers PCB Layout using Altium Designer

4-Layers PCB Layout using Altium Designer

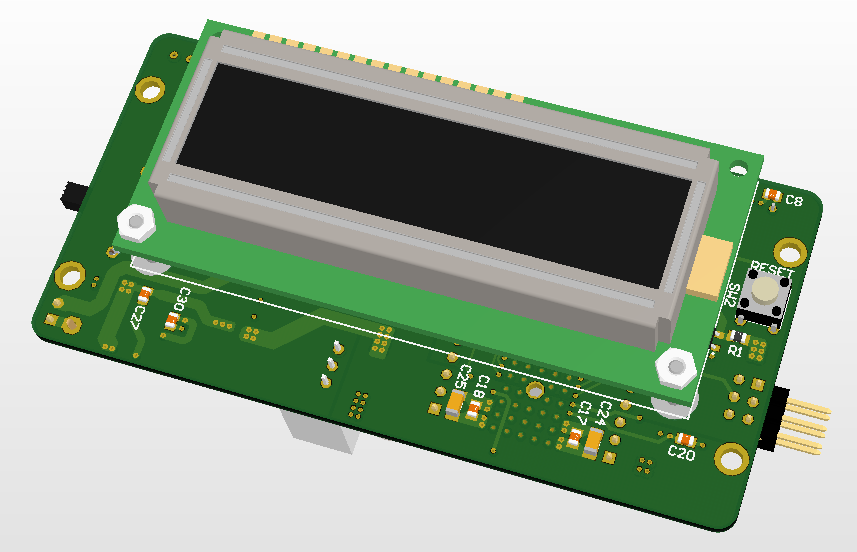

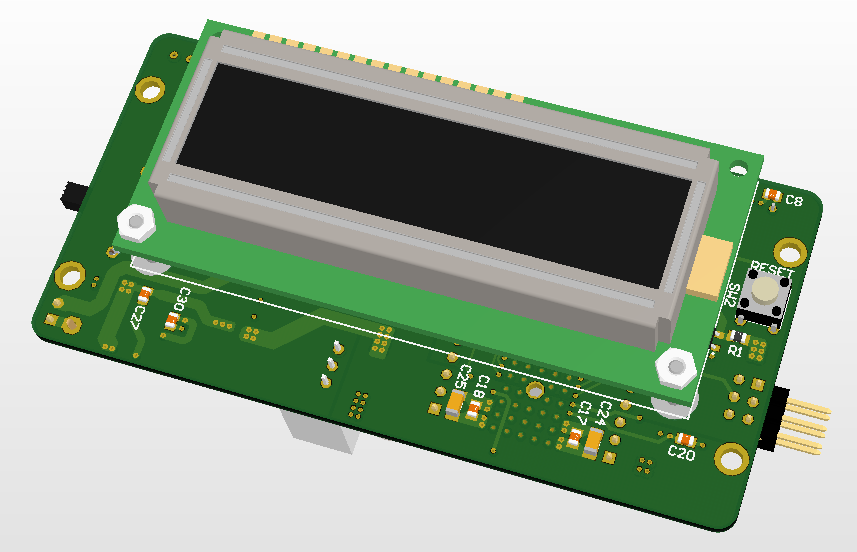

RFID project

Quadcopter Controller Board

Quadcopter Controller Board

Magnet Controller using Android Apps - Shipped to US

Universal Remote + Camera + Wifi Module

Universal Remote + Camera + Wifi Module

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

AD7763EDZ Analog to Digital Board PCB layout

4-Layers PCB Layout using Altium Designer

4-Layers PCB Layout using Altium Designer

RFID project

レビュー

変更を保存しました

1 - 5 / 50+ レビュー表示中

$270.00 USD

C Programming

Engineering

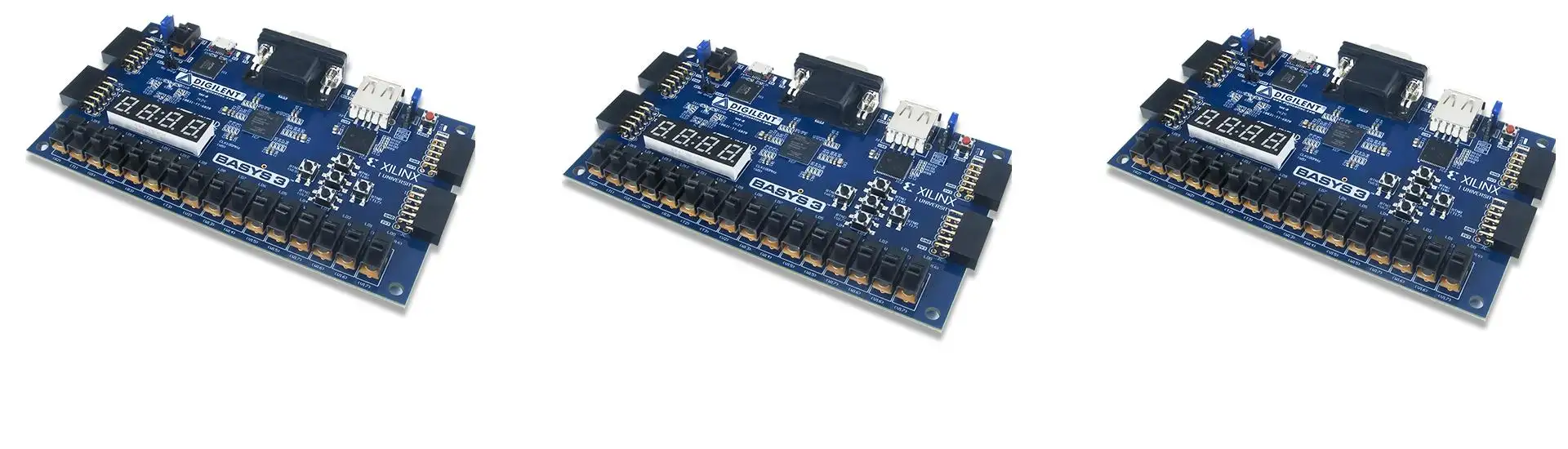

Verilog / VHDL

Electrical Engineering

FPGA

A

•

$70.00 CAD

Electronics

Verilog / VHDL

Electrical Engineering

Digital Design

•

$200.00 CAD

Electronics

Verilog / VHDL

Electrical Engineering

Arduino

FPGA

G

•

$150.00 USD

Electronics

Verilog / VHDL

Electrical Engineering

Digital Design

+1 もっと

J

•

$80.00 USD

Electronics

Verilog / VHDL

Electrical Engineering

Digital Design

+1 もっと

J

•

経験

FPGA/Verilog/VHDL Developers

1月 2018 - 現在

Founder of FPGA4student. An experienced FPGA/Verilog/VHDL Engineer with more than 6 years experience and hundreds of FPGA projects in Verilog/ VHDL, Digital Logic/Circuit/System Design in LogiSim/CEDAR, and MIPS Assembly.

Expertise: Xilinx ISE, Vivado, Quartus, Modelsim, Logisim, CEDAR, Qtspim, MARS, PSpice, Altium, OrCAD, Proteus, Arduino.

Founder

11月 2016 - 現在

FPGA4student where shares free FPGA/Verilog/VHDL source code/ projects/ tutorials with EEE students.

Also offering FPGA/Verilog/VHDL Design/ Tutoring/ Consulting Services.

Experienced FPGA/Verilog/VHDL Engineer

8月 2014 - 現在

An experienced FPGA/Verilog/VHDL engineer with more than 6 years experiences on FPGA Design using Verilog/ VHDL, digital logic design LogiSim, Circuit design, MIPS Assembly, etc.

教育

IC Design Course

(1 )

Bachelor of Engineering

(5 )

資格

IC Design Course Completion

Synopsys

2014

IC Design Course using Synopsys Design Tools

Odon Vallet scholarship

Prof. Odon Vallet and "Meeting Vietnam" Organization

2013

Scholarship for best performed students in central region of Vietnam in 2013

Intel Vietnam Engineering scholarship

Intel Vietnam

2012

Scholarship for top engineering students at DUT in 2011 and 2012

出版物

A FPGA-Based Embedded Fingerprint Identification System

the 2014 National Conference on Electronics, Communications and Information Technology – REV-ECIT 2014

A FPGA-Based Embedded Fingerprint Identification System on the 2014 National Conference on Electronics, Communications and Information Technology – REV-ECIT 2014

A FPGA-Based Embedded Fingerprint Identification System

The University of Danang

A FPGA-Based Embedded Fingerprint Identification System

仕事についてLoi L.に連絡する

ログインしてチャットで詳細を相談しましょう、

認証

認定

トップスキル

同じようなショーケースを検索

招待状の送信に成功しました!

ありがとうございます!無料クレジットを受け取るリンクをメールしました。

メールを送信中に問題が発生しました。もう一度お試しください。

プレビューを読み込み中

位置情報へのアクセスが許可されました。

あなたのログインセッションの有効期限がきれ、ログアウトされました。もう一度ログインしてください。