あなたはをフォローしました

ユーザーのフォローエラー。

このユーザーはフォローを許可していません。

このユーザーをすでにフォローしています。

あなたのメンバーシッププランは、0 個のフォローのみ許可します。アップグレードは、 こちら。

のフォローを解除しました

ユーザーのフォロー解除エラー。

あなたはを推薦しました

ユーザーの推薦エラー。

何か問題が発生しました。ページを更新してもう一度お試しください。

仕事についてMohamed M.に連絡する

ログインしてチャットで詳細を相談しましょう、

ポートフォリオ

ポートフォリオ

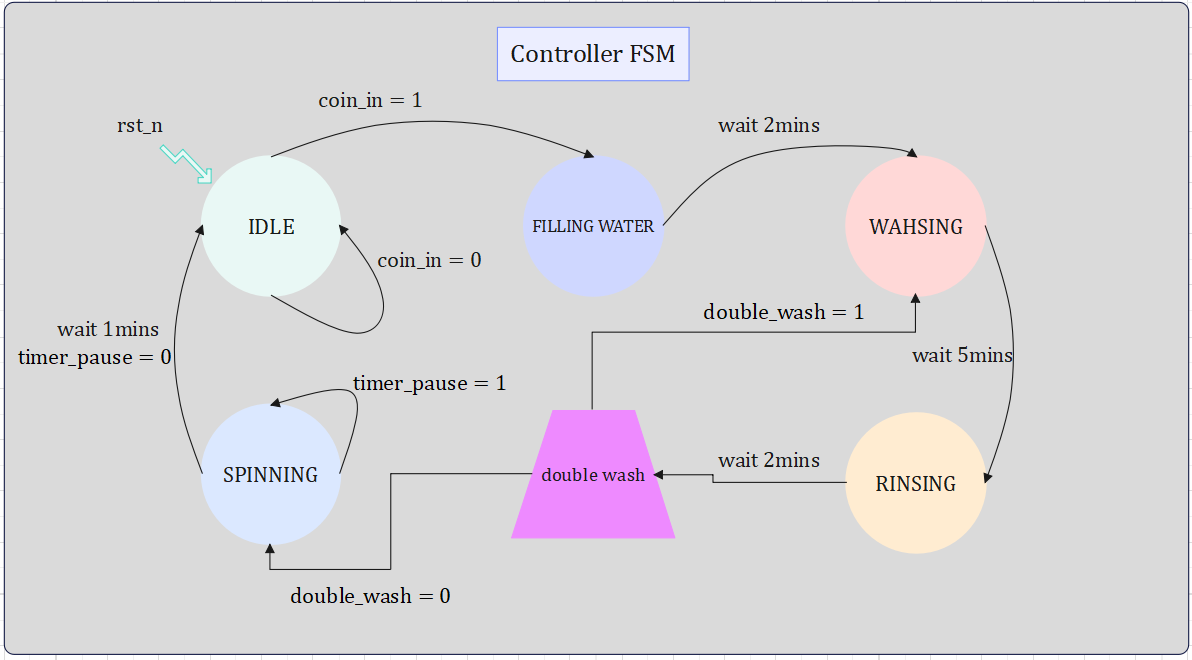

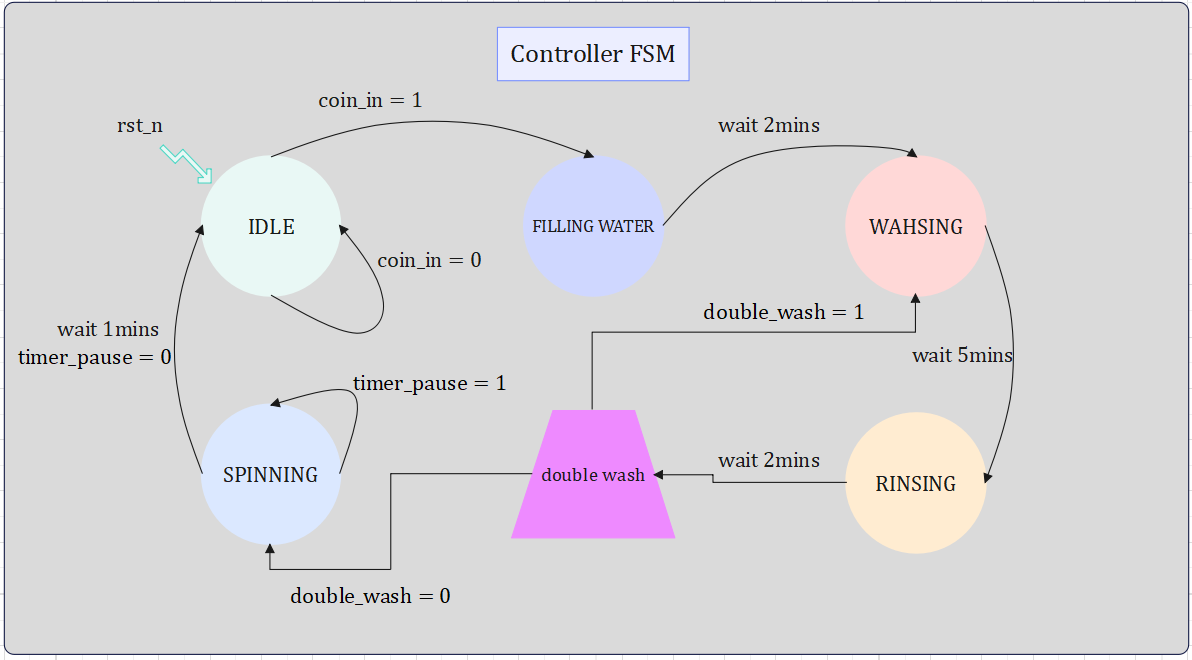

Washing Machine Controller, using Verilog HDL.

Washing Machine Controller, using Verilog HDL.

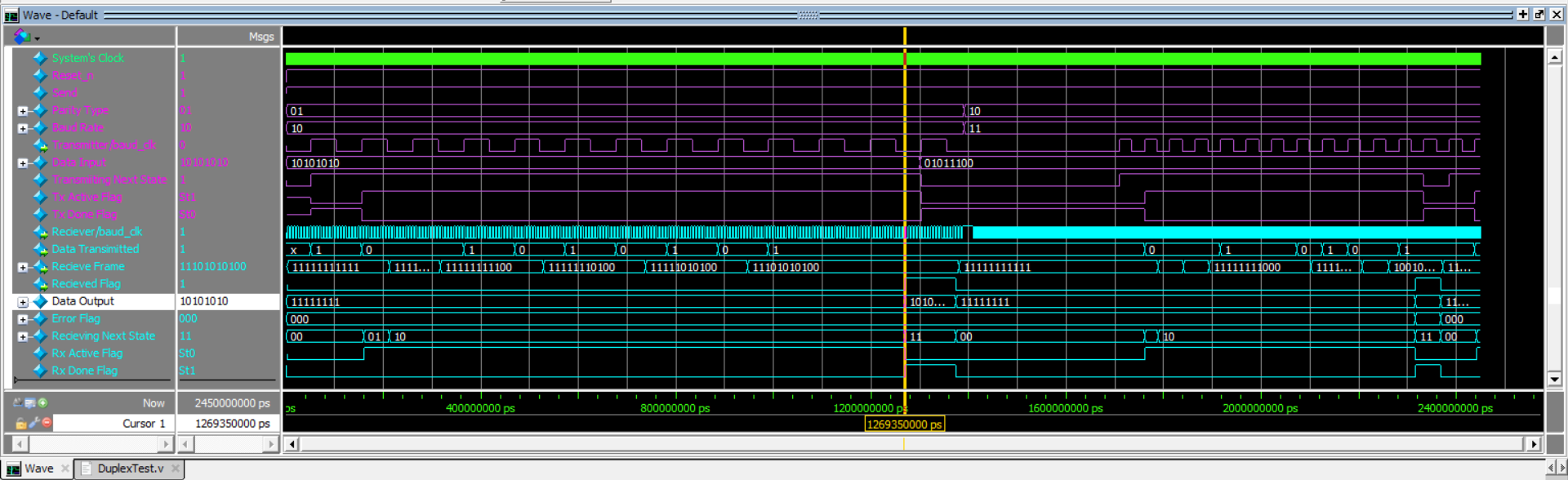

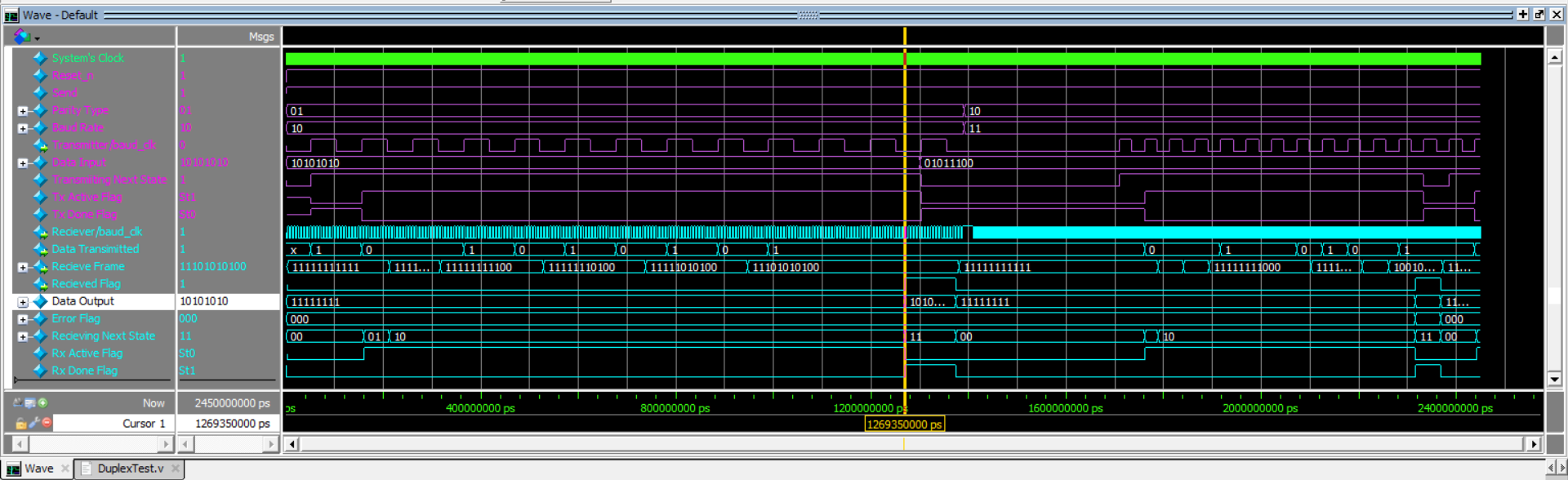

Full UART implementation using Verilog HDL

Full UART implementation using Verilog HDL

Full UART implementation using Verilog HDL

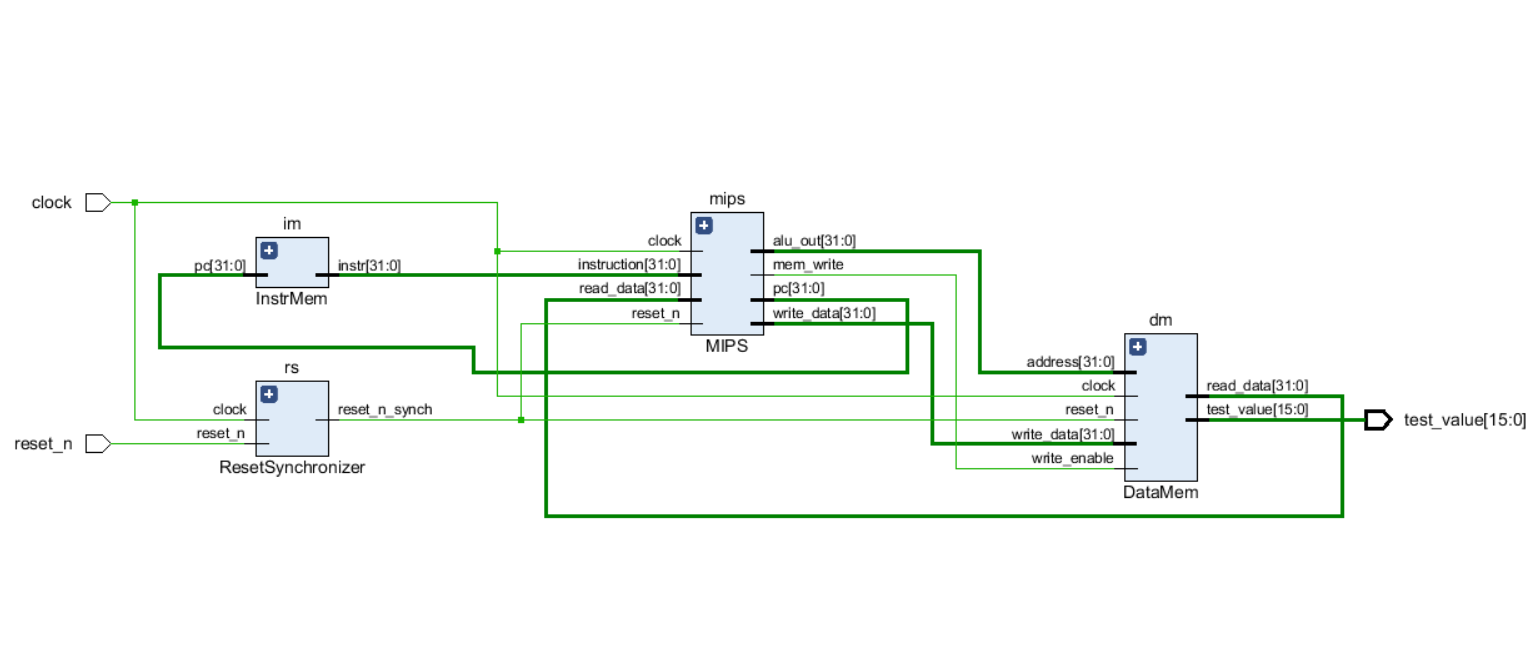

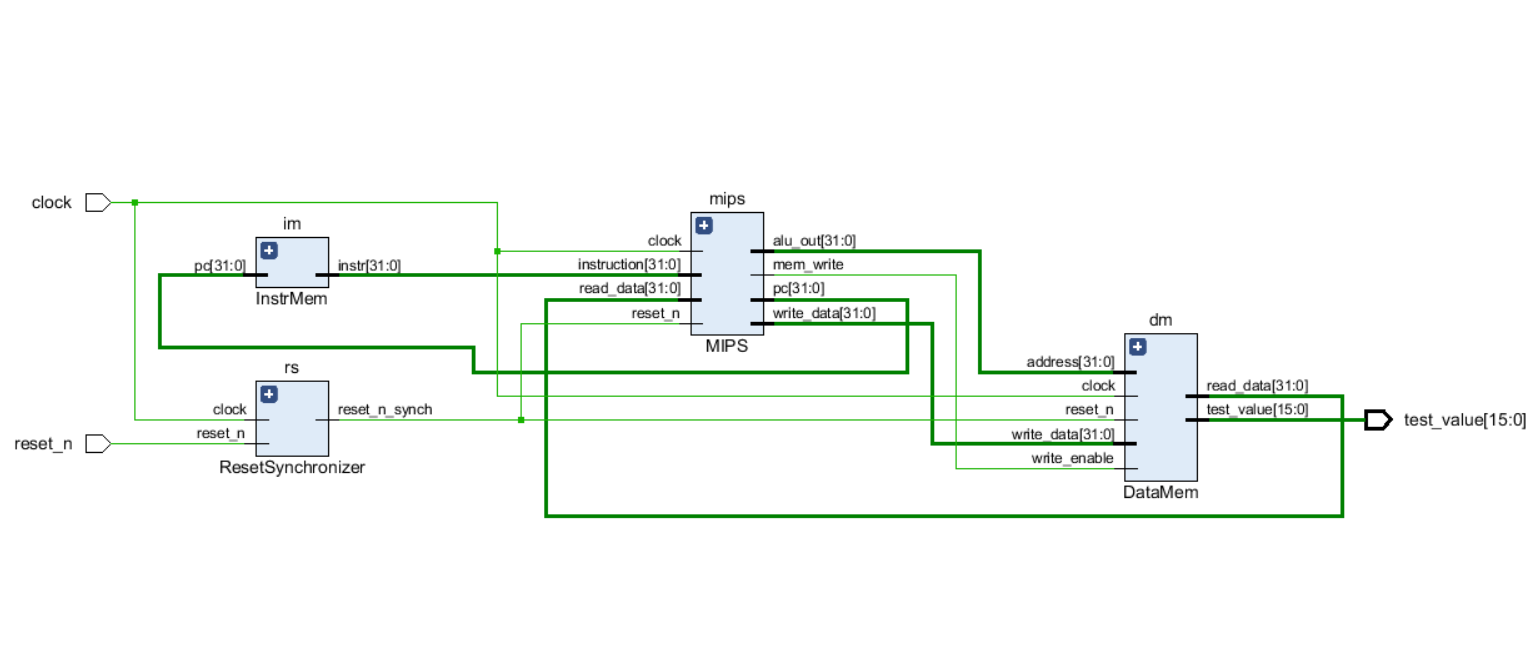

Implementation of 32-bit MIPS-processor using SystemVerilog

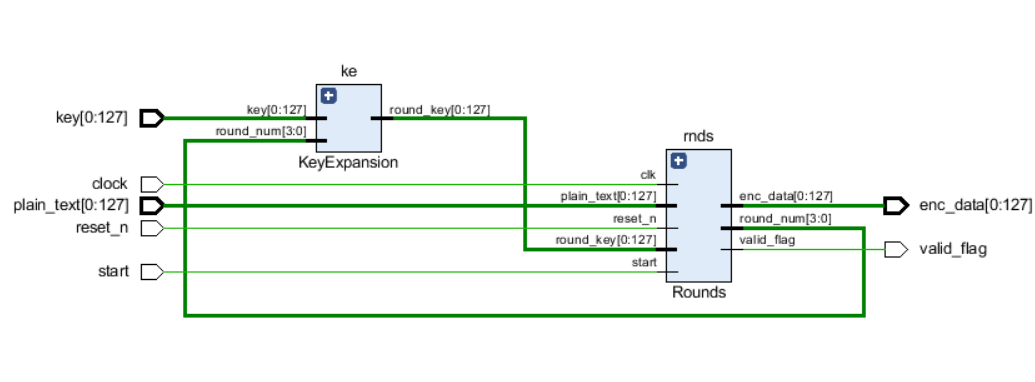

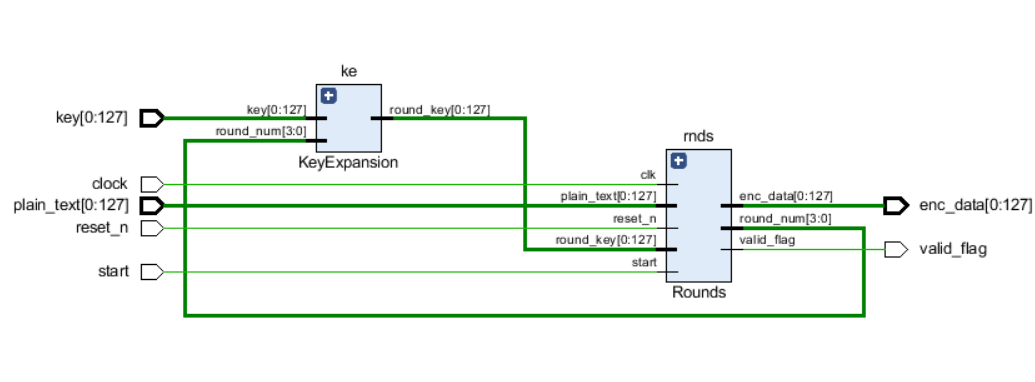

Advanced Encryption Standard (AES) modelling, using Verilog

Washing Machine Controller, using Verilog HDL.

Washing Machine Controller, using Verilog HDL.

Full UART implementation using Verilog HDL

Full UART implementation using Verilog HDL

Full UART implementation using Verilog HDL

Implementation of 32-bit MIPS-processor using SystemVerilog

Advanced Encryption Standard (AES) modelling, using Verilog

レビュー

変更を保存しました

レビューがありません!

経験

Digital IC Design and Verfication

3月 2022 - 現在

◦ Efficient Synthesizable RTL coding: using Verilog/SystemVerilog HDLs

◦ Computer Architecture: Undersatnding of the under-hood of the computer by studying the MIPS processor architecture

and designing it by SystemVerilog HDL.

◦ Verification: Understanding of the basic concepts of verification using SystemVerilog HDL.

Digital IC Design with FPGA

8月 2022 - 11月 2022 (3 , 1 )

◦ Efficient Synthesizable RTL coding: using Verilog HDL, Self-test test benches.

◦ Synthesis and implementation: used Xilinx ISE to implement the design on Spartan-6, I/O

planning layout using the PlanAhead tool, tested the design with multiple clock domains and applied to time

constraints.

◦ Acceleration FPGA Design: used Vivado IDE to implement the design on the Zynq-7000 board, used the logic analyzer to debug the design and created IP then used the IP integrator to create a block design.

教育

Bachelor degree of Electronics and Electrical Communication Engineering

(4 )

資格

Digital Design with FPGA

NajahNow, One Lab, Zewail City

2022

- Efficient Synthesizable RTL coding: using Verilog HDL, verified by Self-test test-benches.

- HDL Synthesis and implementation on FPGA: used Xilinx ISE to implement the design on Spartan-6 FPGA, I/O planning layout for pin assignment using PlanAhead tool, tested the design with multiple clock domains, and applied timing constraints.

- Acceleration FPGA Design: used Vivado IDE to implement the design on the Zynq-7000 board.

仕事についてMohamed M.に連絡する

ログインしてチャットで詳細を相談しましょう、

認証

同じようなショーケースを検索

招待状の送信に成功しました!

ありがとうございます!無料クレジットを受け取るリンクをメールしました。

メールを送信中に問題が発生しました。もう一度お試しください。

プレビューを読み込み中

位置情報へのアクセスが許可されました。

あなたのログインセッションの有効期限がきれ、ログアウトされました。もう一度ログインしてください。